Fonctionnement du CCD

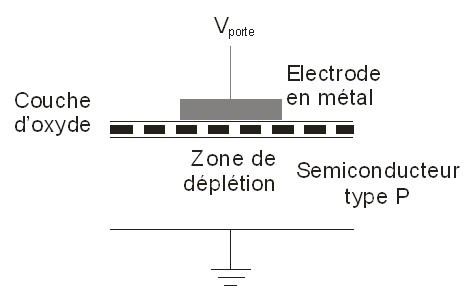

La technologie de base sur laquelle repose le CCD est la capacité MOS (Metal Oxyde Semiconductor) (Fig.3). Si un photon dont l'énergie est supérieure à l'énergie du gap est absorbé dans la zone de déplétion, il produit une paire électron-trou. L'électron reste dans la zone de déplétion tandis que le trou se dirigera vers l'électrode de terre. La quantité de charge négative (électrons) qui peut être collectée est proportionnelle à la tension appliqué, à l'épaisseur d'oxyde et à la surface de l'électrode de porte. Le nombre total d'électrons qui peut être stocké est appelé contenance du puits (« well capacity »). Quand la longueur d'onde augmente, les photons sont absorbés à une profondeur croissante. Ceci limite notamment la réponse aux longueur d'onde élevées. On dispose actuellement de capteurs pouvant fonctionner de l'infrarouge lointain aux rayons X.

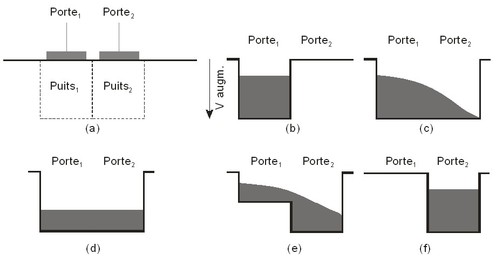

Le registre CCD consiste en une série de portes. La manipulation de la tension de porte, d'une manière systématique et séquentielle, transfère les électrons d'une porte à l'autre à la manière d'un convoyeur. Pour le transfert de charge, les zones de déplétion doivent se chevaucher (Fig.4.a). Les zones de déplétion sont en gradient et les gradients doivent se chevaucher pour que le transfert de charge se produise.

Chaque porte a sa propre tension de contrôle qui varie en fonction du temps. La tension est un signal carré qui est appelé horloge, ou signal d'horloge. Au départ, une tension est appliquée à la porte 1 et les photoélectrons sont collectés dans le puits 1 (b). Quant une tension est appliquée à la porte 2, les électrons se déplacent vers le puits 2 à la manière d'une cascade (c). Ce processus est rapide et la charge s'équilibre rapidement dans les deux puits (d). Lorsque la tension est réduite à la porte 1, le puits de potentiel décroît et les électrons s'écoulent à nouveau en cascade dans le puits 2 (e). Finalement, lorsque la tension de la porte 1 approche de zéro, tous les électrons sont dans le puits 2 (f). Ce processus est répété plusieurs fois jusqu'à ce que la charge soit transférée à travers tout le registre à décalage. Lorsque la tension de porte est basse, elle agit comme une barrière tandis que lorsque la tension est élevée, la charge peut être stockée.

Un pixel peut être constitué de plusieurs portes (de 2 à 4, voire plus), encore parfois appelées phases du système. En fonction des signaux d'horloges (cf. infra), et à taille de pixel égale, 50% de la surface du pixel est disponible pour le puits dans un système à quatre phases, contre 33% dans un système à 3 phases.

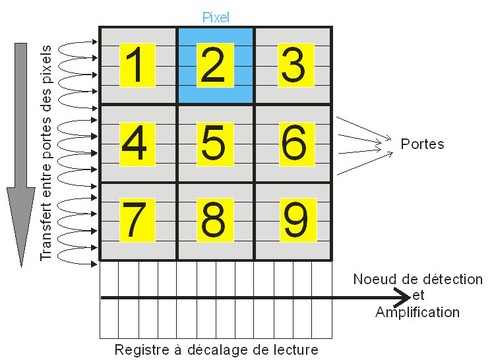

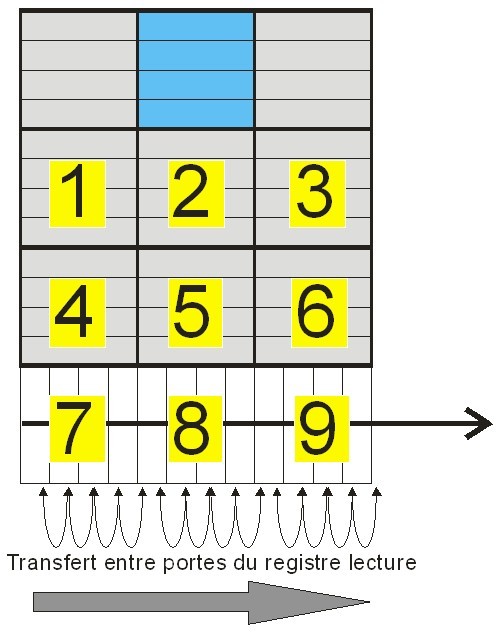

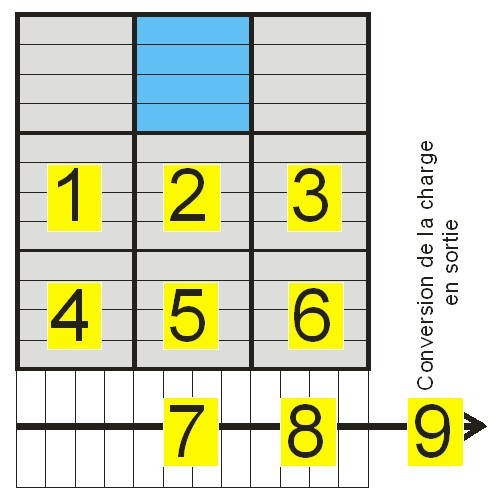

La matrice CCD est une série de registres en colonnes (Fig.5). Après l'exposition et génération de charge par effet photoélectrique pour chaque pixel, la charge est conservée dans les lignes ou dans les colonnes par des canaux ou des blocs d'arrêt et les régions de déplétion ne se chevauchent que dans une seule direction (descendante pour les colonnes, et horizontale pour la ligne de lecture). Le transfert de charges s'effectue d'abord de ligne à ligne par les sauts des portes intra puis inter-pixels (Fig.6). A la fin de chaque colonne se trouve un registre horizontal de pixels. Ce registre collecte une ligne à la fois puis transporte les paquets de charge en mode série vers un amplificateur de sortie. L'entièreté du registre série horizontal doit être synchronisé avec le nœud de détection avant que la ligne suivante n'entre dans le registre série (Fig.6). Pour cela des horloges verticales et horizontales séparées sont requises pour toutes les matrices.

L'interaction entre plusieurs milliers de transferts réduit le signal de sortie. La capacité à transférer la charge est spécifiée par l'efficacité de transfert de charge (CTE). Bien que l'on puisse utiliser un nombre quelconque de sites de transfert (portes) par pixel à la surface du détecteur, on en utilise généralement de deux à quatre, voire même un système à phase virtuelle qui ne demande qu'une seule horloge.

Pour chaque système mentionné, l'étape finale du processus est de convertir le paquet de charge en une tension mesurable. Ceci est réalisé par une diode flottante ou une diffusion flottante. La diode, agissant comme un condensateur, génère une tension proportionnelle au nombre d'électrons, ne. Le signal peut ensuite être amplifié, traité et encodé numériquement par des processeurs électroniques indépendants du détecteur CCD.

Avec plusieurs matrices, il est possible de déplacer plus d'une ligne de charge dans le registre série. Similairement, il est possible de déplacer plus d'un élément du registre série dans une porte de sommation juste avant le noeud de sortie. Ceci est appelé groupement de charge, « binning », « super pixeling », ou encore « agrégation de charges ». Le binning augmente le signal de sortie et la dynamique du signal, mais au détriment de la résolution spatiale du capteur. Parce qu'il augmente le rapport signal sur bruit, le binning est intéressant pour des applications à faible niveau lumineux dans des cas où la résolution est peu importante. Les registres série et le nœud de sortie demandent des puits d'une contenance de charge plus élevée pour le binning. Si le condensateur de sortie n'est pas rafraîchi après chaque pixel, alors il peut accumuler la charge.